# 单口工业以太网百兆 PHY

### 1. 特征

- ► MAC 接口 MII/RMII;支持 3.3V

- ▶ 支持 100BASE-TX; 10BASE-Te

- ▶ 支持 EtherCAT:

- ▶ 低延迟 Latency Tx 54ns, Rx 190 ns

- ▶ 确定性 Latency < ±2ns, Power cycles

- ▶ XI与 TX CLK 相位差抖动 < ±2ns

- ► 优异的 ESD 特性:

- ► MDI 管脚 HBM ESD rating ±10kV

- ▶ 非 MDI 管脚 HBM ESD rating ±8kV

- ▶ 自协商、强制模式下均支持线序与极性自适应

- ▶ 默认 Fast link down 功能

- ▶ 硬件管脚配置工作模式

- ▶ 多种复位、休眠模式

- ▶ 两路 LED 显示状态可配置

- ▶ 多种方式的自诊断、调试检测

# 2. 应用场景

- ▶ 伺服驱动

- ▶ 工厂自动化

- ▶ 轨道交通

- ▶ 医疗检测设备

- ▶ 打印机等办公设备

- ▶ 通信设备

- ▶ 电力监控

# MDC REGIN AVDD33 DVDD33 REGOUT AVDD12 MDIO RESET RESET LED1 1% RESET LED2 AND AVDD33 DVDD33 REGOUT AVDD12

图1 典型应用

## 3. 概述

LY1210A 是一款为适应复杂、苛刻工业应用环境而特别设计的单口百兆 PHY。它兼容MII、RMII 接口,在 MII 模式下,具备优秀的Latency 延迟特性,尤其适合 EtherCAT 应用。

LY1210A 只需要一路 3. 3V 外置电源供电,内部产生 1. 2V 供 core 模块使用(也支持外置 1.2V)。在 100M 速率下,芯片典型功耗 218mW。

LY1210A 主要设计用于工业以太网应用, 具备优秀的抗干扰能力,能适应不同复杂的工 业环境。

LY1210A 具备 MDI 线序以及 MDI 正负极性识别的功能,使得应用简易方便。

LY1210A 有多种硬件配置模式,上电即可正常工作,无需 MDIO 额外配置。

LY1210A 集成网络唤醒 WOL 与 EEE 节能功能。

LY1210A 采用 QFN 5mm×5mm, 32 管脚封装。

Linkyum LY1210A

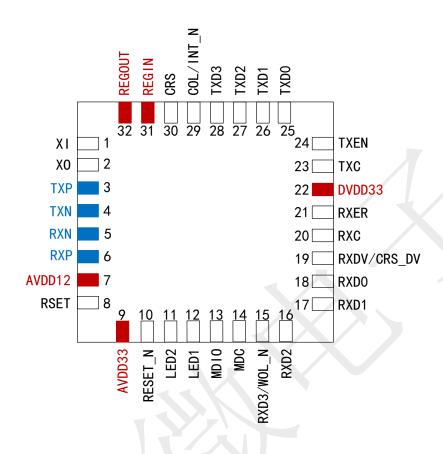

# 4. 封装管脚

图 2 封装管脚

# 5. 管脚描述

### 管脚类型

| 目脚矢至                    |    |          |  |  |  |

|-------------------------|----|----------|--|--|--|

| 管脚类型说明                  |    |          |  |  |  |

| 序号                      | 类型 | 说明       |  |  |  |

| 1                       | 1  | 输入       |  |  |  |

| 2                       | 0  | 输出       |  |  |  |

| 3                       | 10 | 输入输出双向   |  |  |  |

| 4                       | OD | 开漏输出     |  |  |  |

| 5                       | PU | 内部集成上拉电阻 |  |  |  |

| 6                       | PD | 内部集成下拉电阻 |  |  |  |

| 7                       | S  | 上电配置检测管脚 |  |  |  |

| 8                       | В  | 偏置管脚     |  |  |  |

| 9 PWR                   |    | 电源管脚     |  |  |  |

| 10 GND                  |    | 接地管脚     |  |  |  |

| PD、PU 集成上下拉电阻,典型值为 75kΩ |    |          |  |  |  |

Linkyum LY1210A

管脚功能描述

|          | 官脚切形抽处     |             |        |                                                 |                   |  |  |  |  |

|----------|------------|-------------|--------|-------------------------------------------------|-------------------|--|--|--|--|

| 管脚<br>类别 | 管脚<br>号    | 名称          | 类型     | 描述说明                                            |                   |  |  |  |  |

| 时钟       | 1          | XI          |        | Crystal 输入或者外灌 clk 信号输入                         |                   |  |  |  |  |

|          |            | 74          |        | Crystal 输出                                      |                   |  |  |  |  |

|          | 2          | хо          | 0      | 当 XI 管脚输入 clk 信号,XO 管脚浮                         | 空                 |  |  |  |  |

|          | 31         | REGIN       | PWR    | 芯片内部 LDO 输入管脚,输入 3.3V                           |                   |  |  |  |  |

|          | 32         | REGOUT      | PWR    | 芯片内部 LDO 输出,输出 1.2V 电压                          |                   |  |  |  |  |

| 电源       |            |             |        | 芯片模拟 1. 2V 电压的输入管脚,                             |                   |  |  |  |  |

|          | 7          | AVDD12      | PWR    | 该管脚接 REGOUT 管脚,或接外置 1.2V                        |                   |  |  |  |  |

|          | 9          | AVDD33      | PWR    | 芯片模拟 3. 3V 电压输入管脚                               |                   |  |  |  |  |

|          | 22         | DVDD33      | PWR    | 芯片数字 3.3V 电压输入管脚                                |                   |  |  |  |  |

| 复位       | 10         | RESET_N     | I PU   | 低电平输入有效,需要保持低电平 10ms                            |                   |  |  |  |  |

|          | 3          | TXP         | Ю      |                                                 |                   |  |  |  |  |

| 媒介       | 4          | TXN         | Ю      | 发送/接收差分对 0                                      |                   |  |  |  |  |

| 接口       | 5          | RXN         | Ю      | 112.14 / Her III 24 / 1 7.1 4                   |                   |  |  |  |  |

|          | 6          | RXP         | Ю      | 发送/接收差分对 1                                      |                   |  |  |  |  |

|          |            |             |        | MII 模式: 100BASE-TX 输出 25M;                      | 10BASE-Te         |  |  |  |  |

|          |            |             |        | 输出 2.5M; TXC 的输出时钟与 XI                          | 时钟具有恒定            |  |  |  |  |

|          |            |             |        | 的相位关系                                           |                   |  |  |  |  |

|          |            |             |        | RMII Master 模式:输出 50M                           |                   |  |  |  |  |

|          |            |             |        | RMII Slave 模式:接收 50M clk,个                      | 作为 phy 的时         |  |  |  |  |

|          | 23         | TXC         | IO PD  | 钟来源                                             |                   |  |  |  |  |

|          | 28         | TXD3        | I PD   | <br>  MII 模式:从 MAC 接收数据                         |                   |  |  |  |  |

|          | 27         | TXD2        | I PD   | RMII 模式: XXD3、TXD2 未使用, TXD1、TXD0<br>从 MAC 接收数据 |                   |  |  |  |  |

|          | 26         | TXD1        | I PD   |                                                 |                   |  |  |  |  |

|          | 25         | TXD0        | I PD   |                                                 |                   |  |  |  |  |

|          | 24         | TXEN        | I PD   | 发送使能,TXEN 为高表示 TXD 线上有发送数据                      |                   |  |  |  |  |

| MII      |            |             |        | MII 模式: 100BASE-TX 输出 25M;                      | 10BASE-Te         |  |  |  |  |

| 接口       |            |             |        | 输出 2. 5M                                        |                   |  |  |  |  |

|          | 20         | RXC         | O PD   | RMII 模式:未使用                                     | <b>I</b>          |  |  |  |  |

| -        | <b>9</b> / |             |        | MII 模式:发送数据                                     | 上电与硬复             |  |  |  |  |

|          | 15         | RXD3/WOL_N  | O PD S | RMII 模式: RXD3 作为 WOL 中断                         | 位期间,              |  |  |  |  |

|          | 16         | RXD2        | O PD S | 输出                                              | Power on          |  |  |  |  |

|          | 17         | RXD1        | O PD S | RXD2 未使用,RXD1、RXD0 向                            | Strapping 管       |  |  |  |  |

|          | 18         | RXD0        | O PD S | MAC 发送数据                                        | 脚作为输              |  |  |  |  |

|          |            |             |        | MII 模式: 作为数据接收有效                                | 入,其余状             |  |  |  |  |

|          |            |             |        | RXDV 信号                                         | 态下作为输             |  |  |  |  |

|          |            |             |        | RMII 模式:作为 CRS_DV 信号;                           | 出管脚<br>Ctrop 功能配  |  |  |  |  |

|          |            |             |        | 可通过寄存器配置,使此管脚在                                  | Strap 功能配<br>置,请见 |  |  |  |  |

|          | 10         | DVDV/CDC DV | 0 00 0 | RMII 模式下,依然作为 RXDV 信                            | 直,                |  |  |  |  |

|          | 19         | RXDV/CRS_DV | O PD S | 号                                               | I OMEL OIL        |  |  |  |  |

Linkyum LY1210A

|     |    |           |         | 接收错误信号,RXER 为高表示                      | Strapping 部 |

|-----|----|-----------|---------|---------------------------------------|-------------|

|     |    |           |         | phy 检测到接收错误(在 RXDV 为                  | 分详细介绍       |

|     | 21 | RXER      | O PD S  | 高时)                                   |             |

|     |    |           |         | 载波侦测信号,MII 半双工模式下                     |             |

|     |    |           |         | 有效;                                   |             |

|     | 30 | CRS       | O PD S  | RMII 模式该管脚未使用                         |             |

|     |    |           |         | 冲突检测信号,MII 半双工模式下                     |             |

|     |    |           |         | 有效;                                   |             |

|     |    |           |         | RMII 模式下,该管脚作为中断输                     |             |

|     | 29 | COL/INT_N | O PD S  | 出                                     |             |

| 13  |    | MDIO      | IO PU   | 管理数据接口 MDIO,与 MDC 时钟同                 | 涉           |

|     | 14 | MDC       | I PU    | 管理数据接口 MDC,最高频率 2.5M                  |             |

| LED | 12 | LED1      | OD PU S | <br>  LED 状态输出<br>  上电与硬复位期间,检测管脚状态,以 | 以确定LED      |

|     | 11 | LED2      | OD PU S | pin 作为 Sink 或 Sourcing 模式             | A HOUR LLD  |

| 基准  |    |           |         | XA                                    |             |

| 偏置  | 8  | RSET      | В       | 接 1% 精度的 12k 电阻到地                     |             |

| 地   | EP | EPAD      | GND     | 热焊盘芯片地                                |             |

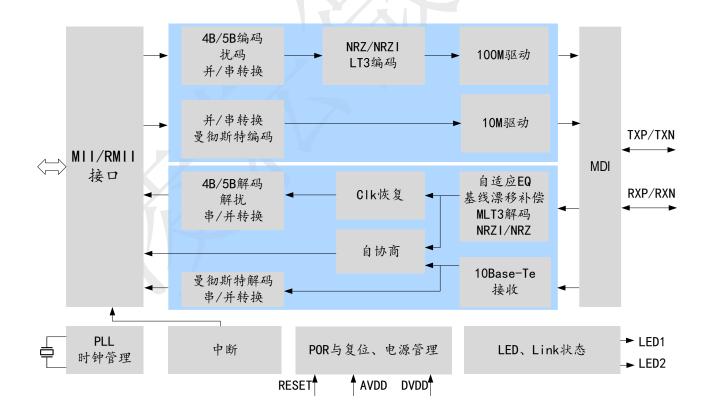

# 6. 功能框图

图 3 功能框图